Inicio / Archivo / Año 3, No 3, septiembre 2020 - agosto 2021 / Paper 08

ARQUITECTURA RECONFIGURABLE EN FPGA PARA UN

DEMAPPER DE TIPO HARD/SOFT DECISION PARA

CONSTELACIONES BPSK/QAM-4/16/64/256

Dagoberto Alvarez-Ibarra* y Eduardo Romero-Aguirre*

Instituto Tecnológico de Sonora

*dago1810@hotmail.com,

eduardo.romero@itson.edu.mc

Resumen

El gran auge y demanda de las comunicaciones inalámbricas que se tienen en la actualidad, han motivado que los investigadores incrementen sus esfuerzos en la búsqueda de: algoritmos más eficientes, mejores técnicas de diseño digital y nuevas alternativas tecnológicas para el diseño e implementación de tales sistemas con altas velocidades y altos volúmenes de información. Con ese mismo tenor, en este trabajo se presenta el desarrollo de una arquitectura digital compacta en aritmética de precisión finita, codificada en Verilog y sintetizada en FPGA para el bloque “demapper” de un demodulador. Debido a que dicho bloque es pieza fundamental en cualquier sistema receptor inalámbrico y que su rendimiento impacta directamente en el sistema entero, se optó por diseñar una sola arquitectura compacta que abarque ambos tipos de operación (“hard/soft-decision”), en lugar de la solución convencional de emplear bloques separados por cada tipo. Lo anterior, efectivamente, reduce el consumo de recursos de “hardware” utilizados y, en consecuencia, la energía consumida por el dispositivo. Adicionalmente, la arquitectura digital desarrollada es lo suficientemente flexible para modificar al vuelo tanto su forma de operar como el orden de la constelación deseada (BPSK, QAM-4, 16, 64 y 256) en el modulador. Finalmente, el “demapper” se sintetizó en una tarjeta de desarrollo AC701 de Xilinx alcanzando una frecuencia máxima de operación superior a los 80 MHz con la utilización de recursos menores al 2 %. Todo esto le permite al bloque ser incorporado en cualquier sistema receptor que trabaje con los estándares actuales de comunicación.

Palabras clave: Diseño Digital en FPGA, Comunicaciones Inalámbricas, Soft-Decision, Hard-Decision.

Introducción

En la actualidad, la interacción (casi siempre inadvertida) con las comunicaciones inalámbricas se ha convertido en una actividad cotidiana de gran parte de la población. Por este motivo, existe la necesidad continua de transmitir y recibir información a altas velocidades, con buena calidad y sin comprometer el ancho de banda. Existen varias técnicas que permiten la utilización de banda amplia con manejo eficiente del espectro, tales como: la multiplexación por división de frecuencias ortogonales (OFDM, por sus siglas en inglés) en conjunto con el uso de constelaciones de modulación de amplitud en cuadratura (QAM, por sus siglas en inglés) de alto orden. Como consecuencia, su correcto diseño empleando la tecnología adecuada impactará en su desempeño y por ende en el sistema completo.

Por otro lado, la industria de los semiconductores ha mostrado un incremento exponencial en las últimas décadas en lo que respecta a la complejidad en “hardware” y el desempeño de este (Vaishnav et-al., 2018). Por lo que, las arquitecturas digitales en esta tecnología son una opción atractiva desde el punto de vista de costo-desempeño para desarrollar en forma digital cualquiera de las etapas de un sistema de comunicación (Artetxe, 2013).

Los estándares de comunicación actuales, tales como 5G u 802.11p, que consisten en el uso de técnicas de radio para la transmisión de datos a distancias cortas entre unidades de radio móviles y fijas (Innovation Science and Economic Development Canada, 2017), requieren que sus etapas de transmisión y recepción sean 100 % digitales para cumplir con los requerimientos de velocidad y consumo de potencia, por lo que, el bloque “demapper” QAM no es la excepción, ya que es parte vital en cualquier receptor inalámbrico sin importar si es de portadora única o multiportadora.

Fundamentación teórica

Un sistema de comunicación tiene el propósito de la transmisión de señales de un punto a otro y generalmente se conforman principalmente por tres partes: transmisor, canal de comunicación y receptor. Asimismo, pueden ser de portadora única o multiportadora. Este último permite enviar de manera simultánea información por medio de varias frecuencias utilizando OFDM, lográndose mayores velocidades, mayor ancho de banda y capacidad de afrontar el retardo por multitrayectoria, fenómeno inherente en todos los sistemas de comunicación inalámbricos (Orozco-Galván et-al., 2015). En todo sistema de comunicación, el transmisor contiene el bloque denominado “mapper” y en el receptor su contraparte “demapper”; los cuales son fundamentales para la correcta operación del sistema. El “mapper” se encarga de aceptar una secuencia de bits para agruparlos en subsecuencias de longitud específica asociadas a un punto de la constelación. Por su parte, el “demapper” ejecuta el proceso inverso, con la diferencia que el resultado lo entrega con un criterio tajante (modo “hard”) a nivel de bits (valor de 0 ó 1) o en modo “soft” indicando de forma adicional la probabilidad de que el bit asociado con una salida sea 0 ó 1.

Modelo del sistema

En un modelo del canal ruido blanco aditivo Gaussiano (AWGN, por sus siglas es inglés), la señal recibida r(t) puede describirse matemáticamente como:

r(t)=sm(t)+n(t) (1)

Donde sm(t) es la señal transmitida de las m posibles y n(t) el ruido aditivo. El modelo del canal puede ser reinterpretado matricialmente como:

r=sm+n2 (2)

donde todos los vectores son N-dimensionales. El mensaje m es elegido de acuerdo con la probabilidad del conjunto de posibles mensajes. Los elementos de n son variables aleatorias independientes e idénticamente distribuidas con media cero y varianza N0/2. El vector r depende estadísticamente del vector transmitido a través de las funciones condicionales de probabilidad de densidad p(r|sm). Para minimizar la probabilidad de error, es necesario que se maximice p(r|sm):

m'=argmax1 < m < Mp(sm)=argmin(1<m<M)|r-sm|2 (3)

donde m' es el mensaje elegido, donde el detector recibe r y busca entre todo sm para encontrar el símbolo que se encuentre a la menor distancia utilizando el criterio de distancia euclidiana (Li et-al., 2009)

Modelo para “demapper Hard-Decision”

El caso generalizado QAM M-aria puede ser aplicado a los tipos de constelaciones BPSK (antipodal), QAM-4 (QPSK), 16, 64, 256. La longitud de QAM que es considerada en este documento es M=22n n=1,2,…. El número total de bits en el diagrama de constelación es 2n, donde la primera mitad de bits se obtienen con el “demapper” a partir de la componente en fase (I) de la señal recibida, y la otra mitad con la componente en cuadratura (Q). Con lo que, el procesamiento llevado a cabo en el “hard-demapper” para constelaciones QAM, queda representado con el Algoritmo 1 (Yeh & HongSeok Seo, 2007).

Cabe resaltar que esto mismo aplica para obtener los bits del “demapper” de la componente Q (bQ,k)

Modelo para “demapper Soft-Decision”

Para el caso “Soft-Decision”, los valores generalizados de los bits de la componente en fase (DI,k) se calculan con el algoritmo LLR, el cual de forma generalizada se resume en (Ali et-al., 2015; Tosato & Bisaglia, 2002). De igual forma, esto prevalece para determinar los bits de cuadratura DQ,k, únicamente reemplazando yI[i] con yQ[i] y dI,k con dQ,k):

DI,k={yI[i], k=0 -|DI,k|+dI,k', k=1,21…,n-1 (4)

donde dI,k(o dQ,k) es la mitad de la distancia entre los límites de partición, que son los límites de decisión en algoritmo 1:

dI,k=dQ,k=2n-1, n≥2 (5)

dI,k=dQ,k=2k-1, n≥3 y k=2,3,…,n-1 (6)

donde yI[i] (o yQ[i]) yace fuera de la región “bI,k=1” (o “bQ,k=1”), el signo de DI,k(o DQ,k) será negativo e indica qué tan probable es que bI,k(o bQ,k) sea mapeado a “"0".

El empleo de ambos algoritmos representa de forma teórica, una reducción significativa de la complejidad computacional y con una pérdida insignificante en el rendimiento de la tasa de error de bit (BER, por sus siglas en inglés). Esto los convierte en potenciales candidatos para desarrollarse en forma digital y sintetizarse en un FPGA (“Fiel Programable Gate Array”).

Objetivo

Desarrollar la arquitectura en FPGA de un “demapper” de tipo “hard” y “soft-decision” para las constelaciones “BPSK/QAM-4/16/64/256” que permita a un sistema receptor recuperar fielmente el flujo de información transmitida hacia él.

Metodología

El proceso de diseño es el siguiente (Romero A, 2012):

- Se programa el algoritmo en punto flotante identificando y replicando cada una de sus condiciones de operación.

- Se realiza un análisis del algoritmo para representar sus variables en punto fijo.

- Se diseña una arquitectura digital a nivel caja negra y luego a caja blanca identificando cada uno de los bloques funcionales internos.

- Se modelan cada uno de los bloques requeridos en lenguaje de descripción de hardware (HDL por sus siglas en inglés) Verilog y con la ayuda de la técnica de diseño “Top-Down”.

- Se verifica la arquitectura a través de simulaciones para evaluar su correcto funcionamiento.

- Se sintetiza en FPGA la arquitectura y se simula a través de un entorno de cosimulación, para obtener métricas que evalúen su desempeño, tanto funcional como de implementación.

Todo lo anterior, se acota a la detección de símbolos para las constelaciones BPSK/QAM-4/16/64/256. Además, se presupone que los símbolos han pasado por un proceso de ecualización, es decir, se han restaurado las componentes de frecuencias afectadas por el medio y que la perturbación restante corresponde a la componente de un ruido banco Gaussiano.

Diseño de la arquitectura de hardware

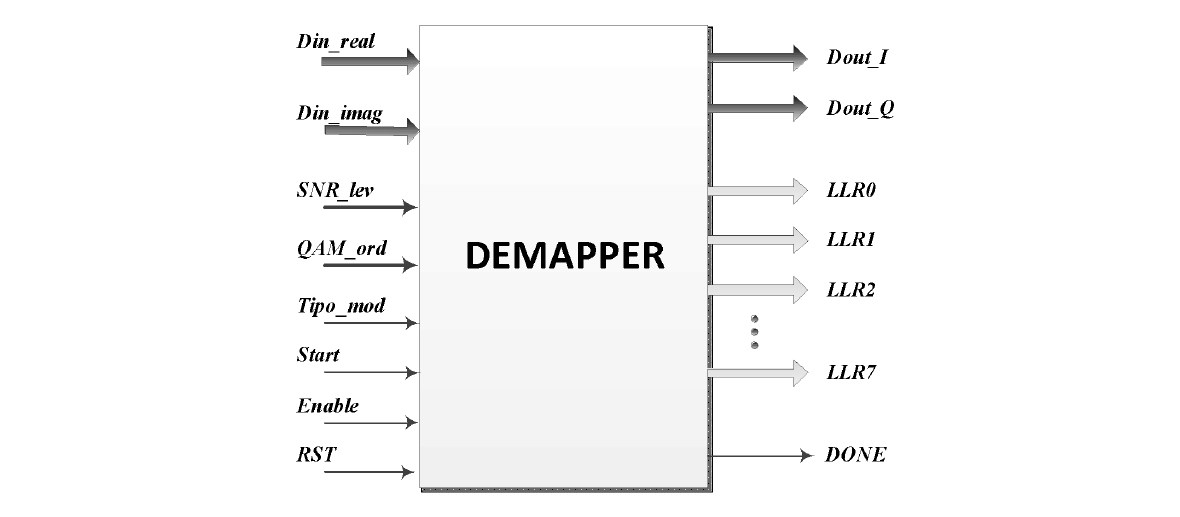

La Figura 1, muestra el diagrama de caja negra del sistema propuesto.

Figura 1: Entradas y salidas del “demapper Hard/Soft-Decision”.

Las entradas D_real y D_imag representan las componentes de la señal recibida r(t), la señal QAM_orden indica el tamaño de la constelación, ent_SNR determina el nivel de SNR a considerar y tipo_mod define el tipo “demapper” a utilizar. Todas las entradas ingresan a los submódulos correspondientes para realizar el proceso indicado en el Algoritmo 1 y las ecuaciones (4) a (6). La salida DONE se activa cuando se tiene una señal de salida válida en los buses de salida, dependiendo del tipo seleccionado. Los buses de salida Dout_I y Dout_Q son de 4 bits en tanto que para el modo “soft” las salidas son los buses de 4 bits LLR0 a LLR7.

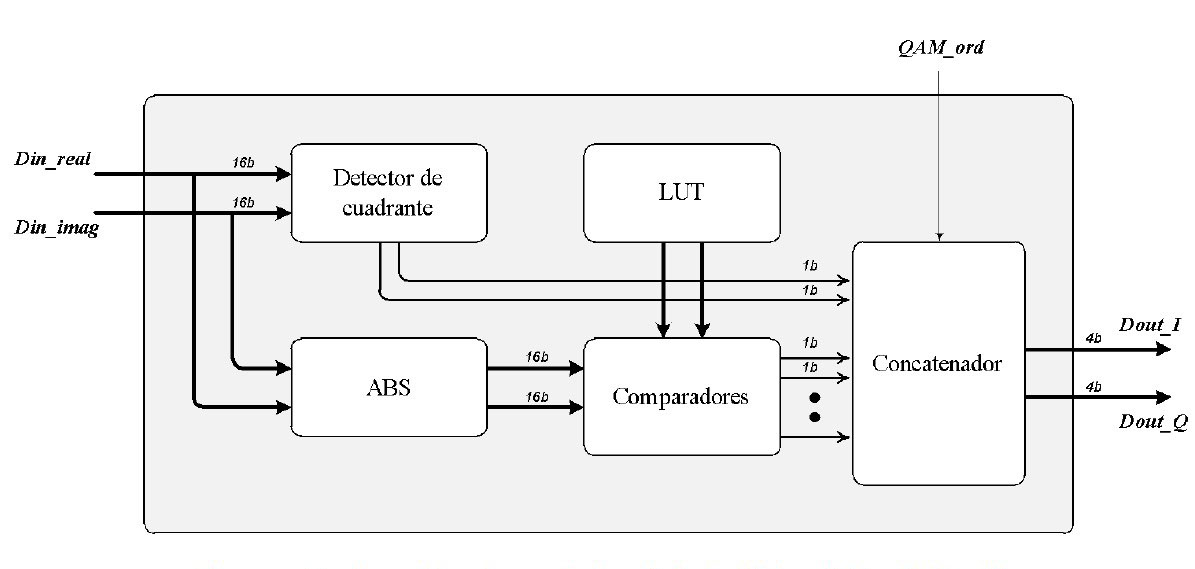

Módulo “Hard-Decision”

Este módulo, a partir de las señales de entrada Din_real, Din_imag, entrega en sus salidas un conjunto de 1’s ó 0’s, que corresponden a un punto específico de la constelación. Para lograrlo, dichas señales se procesan al mismo tiempo en los bloques de detector de cuadrante y el de ABS, que identifican tanto el cuadrante donde se ubica el símbolo recibido como su magnitud, tal como lo sugiere la Figura 2. El bloque comparadores ubica la región específica del símbolo dentro de la constelación con la ayuda de la LUT (“Look-Up Table”), la cual establece de forma dinámica los límites de comparación. Los resultados de las diversas comparaciones se agrupan en el bloque concatenador, acorde a la componente I o Q. Finalmente, estos datos se enrutan a las señales de salida Dout_I y Dout_Q.

Figura 2: Arquitectura del módulo “Hard-Decision”.

Módulo “Soft Decision”

La ejecución en este bloque depende del tamaño de la constelación. El primer valor se obtiene directamente de la señal de Din_real (Din_imag). Este, a su vez, se enruta a través de bloques ABS y sumadores para finalmente escalarse por una constante de la varianza dependiente del nivel de SNR presente en el sistema, tal como puede visualizarse en la Figura 3. El resultado de sus salidas es una palabra digital que representa el valor de bit (1 ó 0) junto con su probabilidad (nivel de confianza) de que así sea.

Figura 3: Arquitectura propuesta de Soft-Demapper.

Resultados y discusión

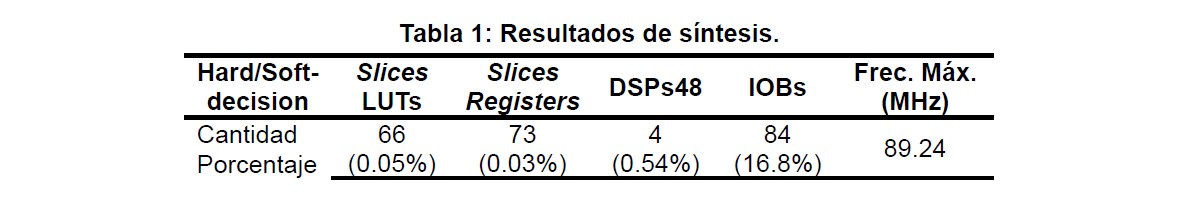

A continuación, se describirán las pruebas realizadas al demapper. Todos los bloques fueron descritos a nivel RTL usando lenguaje Verilog y sintetizados con Vivado 2016.1. La Tabla 1 resume el resultado de este ejercicio, evidenciando un consumo reducido de los recursos del FPGA presente en la tarjeta de desarrollo AC701 de Xilinx.

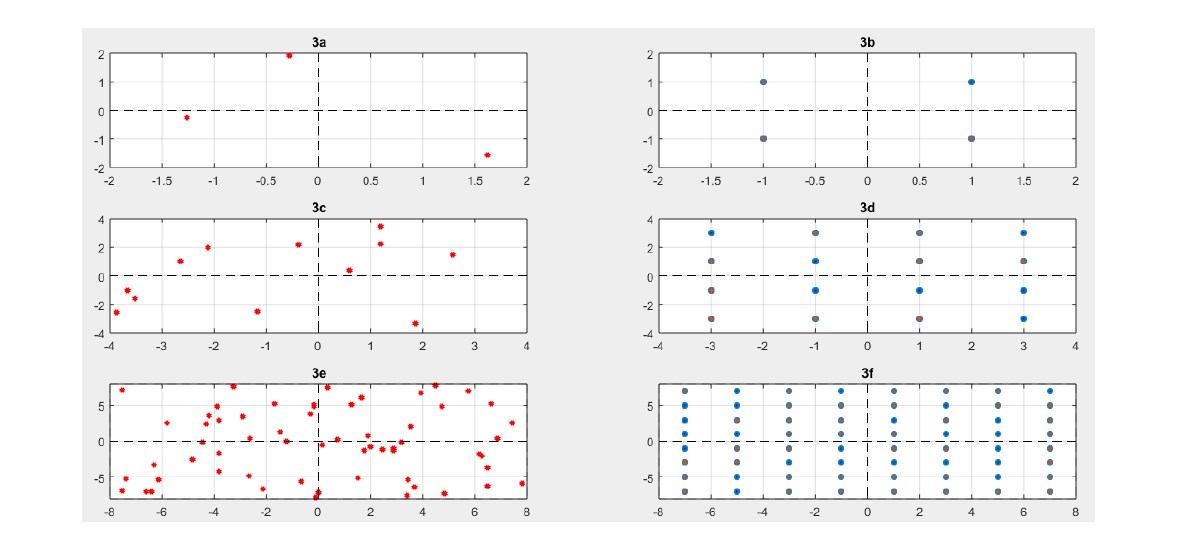

Para el caso de la verificación funcional, se genera un bloque de símbolos aleatorios (Figura 4a, 4c y 4e) y el “demapper” fue capaz de restaurarlos a su posición correcta en la constelación correspondiente (Figura 4b, 4d y 4f).

Figura 4: Bloques de símbolos aleatorios: a) QAM-4, c) QAM-16 y e) QAM-64 entradas; b), d), y f) símbolos de salida restaurados en las mismas constelaciones.

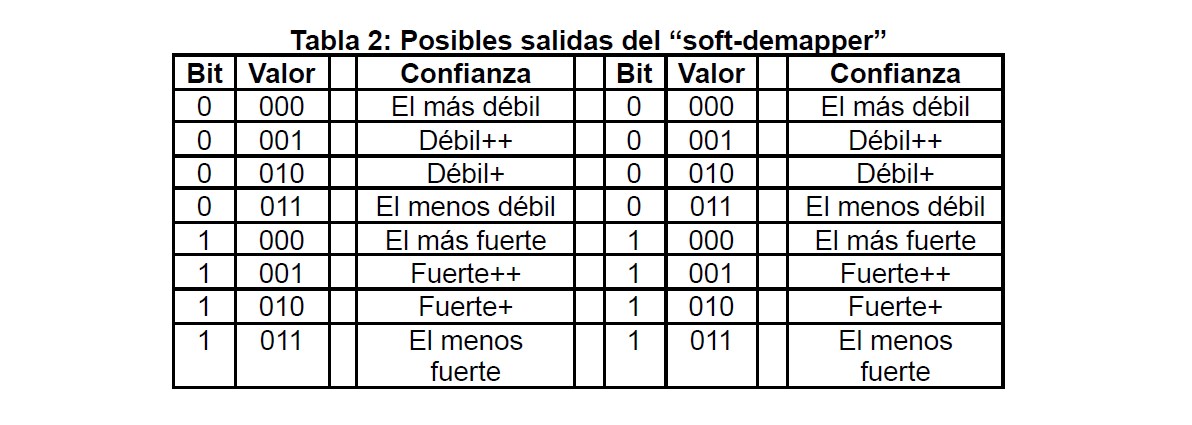

Asimismo, en el caso del “soft demapper” se simuló un proceso similar al del tipo “hard” y se construyó la Tabla 2 con los resultados de sus salidas, la cual resume el funcionamiento que se espera de la arquitectura diseñada.

Conclusiones

El diseño presentado en este artículo demuestra cómo el lenguaje HDL en conjunto con tecnología lógica programable como los FPGAs, constituyen una alternativa para incrementar la capacidad de procesamiento en el diseño digital de sistemas de telecomunicaciones. En nuestro caso, se lograron alcanzar frecuencias de operación >80 MHz, en una arquitectura compacta con baja utilización de recurso de hardware (1%) y con el valor agregado de la configurabilidad (cinco modos de operación). Cabe mencionar que a pesar de que se trabajó con herramientas de Xilinx, la descripción final está libre de librerías o “IP-cores” propietarios, lo que asegura su portabilidad para ser sintetizado en un FPGA’s de cualquier otro fabricante. Para finalizar, es importante también recalcar que el “demapper” es capaz de identificar una gran cantidad de símbolos recibidos, no solo para la constelación de QAM-4, 16 y 64 bits, sino que también nos permite hacerlo para las constelaciones de BPSK, y 256 bits, según sea lo requerido, esto sin la necesidad de aumentar el consumo de los recursos internos del FPGA ni comprometer la velocidad de procesamiento de los datos.

Referencias

- Ali, I., Wasenmüller, U., & Wehn, N. (2015). A high throughput architecture for a low complexity soft-output demapping algorithm. Advances in Radio Science, 13, 73-80.

- Artetxe, I. (2013). Tecnologías actuales para dispositivos lógicos programables [Tesis]. UPV.

- Innovation Science and Economic Development Canada. (2017). Intelligent Transportation Systems—Dedicated Short Range Communications (DSRC)—On-Board Unit (OBU).

- Li, M., Nour, C. A., Jego, C., & Douillard, C. (2009). Design of rotated QAM mapper/demapper for the DVB-T2 standard. 2009 IEEE Workshop on Signal Processing Systems, 018-023.

- Orozco-Galvan, L., Parra-Michel, R., & Romero-Aguirre, E. (2015). Reconfigurable architecture based on FPGA for OFDM transmitter. 2015 7th IEEE Latin-American Conference on Communications (LATINCOM), 1-6.

- Romero A, E. (2012). Arquitecturas digitales de procesamiento de señales para sistemas de comunicación con entrenamiento implicito [Tesis]. Centro de Investigación y de Estudios Avanzados del Instituto Politécnico Nacional.

- Tosato, F., & Bisaglia, P. (2002). Simplified soft-output demapper for binary interleaved COFDM with application to HIPERLAN/2. 2002 IEEE International Conference on Communications. Conference Proceedings. ICC 2002 (Cat. No.02CH37333), 2, 664-668.

- Vaishnav, A., Pham, K. D., & Koch, D. (2018). A Survey on FPGA Virtualization. 2018 28th International Conference on Field Programmable Logic and Applications (FPL), 131-1317.

- Yeh, H.-G., & HongSeok Seo. (2007). Low complexity demodulator for M-ary QAM. 2007 Wireless Telecommunications Symposium, 1-6.

Tercer Congreso Nacional de Tecnología 23, 24 y 25 de septiembre de 2020.

Celebrado en modo virtual.

D. R. © UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO.

Excepto donde se indique lo contrario esta obra está bajo una licencia Creative Commons Atribución No comercial, No derivada, 4.0 Internacional (CC BY NC ND 4.0 INTERNACIONAL).

https://creativecommons.org/licenses/by-nc-nd/4.0/deed.es

ENTIDAD EDITORA

Facultad de Estudios Superiores Cuautitlán.

Av. Universidad 3000, Universidad Nacional Autónoma de México, C.U., Delegación Coyoacán, C.P. 04510, Ciudad de México.

FORMA SUGERIDA DE CITAR:

Alvarez-Ibarra, D., y Romero-Aguirre., E. (2020). Arquitectura reconfigurable en FPGA para un demapper de tipo hard/soft decision para constelaciones BPSK/QAM-4/16/64/256. MEMORIAS DEL CONGRESO NACIONAL DE TECNOLOGÍA (CONATEC), Año 3, No. 3, septiembre 2020 - agosto 2021. Facultad de Estudios Superiores Cuautitlán. UNAM.

https://tecnicosacademicos.cuautitlan.unam.mx/CongresoTA/memorias2020/mem2020_paper12.html